Have you heard about Von Neumann architecture, Harvard Architecture and Non Von Neumann Architecture ?

Von Neumann Architecture

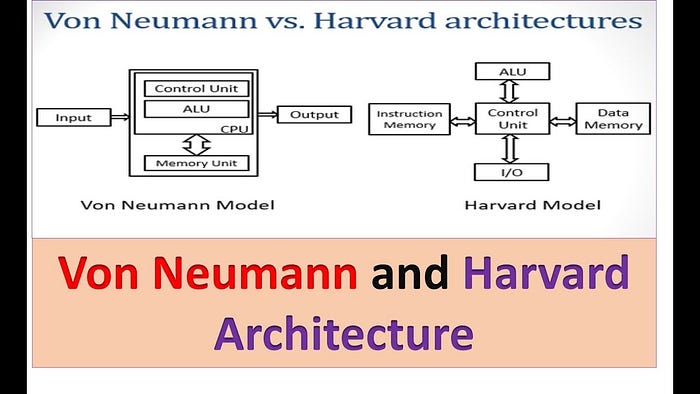

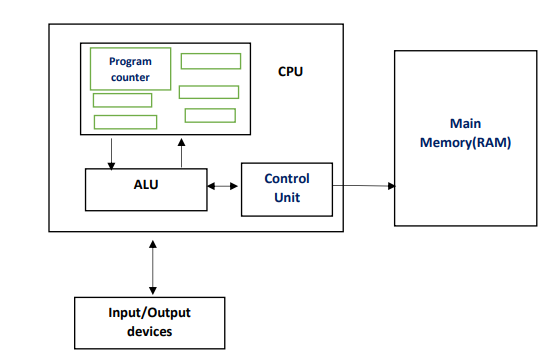

This Von Neumann Architecture was invented by John Von Neumann in 1945. This architecture is based on the stored program counter concept and both the instructions data and program data are stored in the same main memory. This Von Neumann Architecture’s hardware is consisting with, • CPU CPU includes the set of registers (Program counter) Arithmetic and Logic unit, and the control unit. • Main memory system (RAM) • I/O system Main Memory (RAM) Input/Output devices Control Unit ALU Program counter Ac CIR MAR MDR CPU 2 As the input devices keyboard, mouse, scanner, microphone etc and as the output devices monitors, printers, headphones etc. The process of Von Neumann Architecture is, Fetch-Decoding — Execution process.

Fetch

Basically, the thing happen here is the control unit fetches the next instructions from memory (RAM) with the use of program counter in order to illustrate where the instruction is located.

- Program counter which is a special register in CPU stores those memory address.

- This information is very useful for control unit.

- Control unit refers to the memory addresses.

- In a RAM there are data and instructions stored in the memory locations. Those memory locations have a particular memory address.

- To access RAM we need to know the memory address. Main Memory(RAM) Input/Output devices Control Unit ALU Program counter AC CPU 3

- Those addresses are stored in the program counter and we can find them in there.

Decode

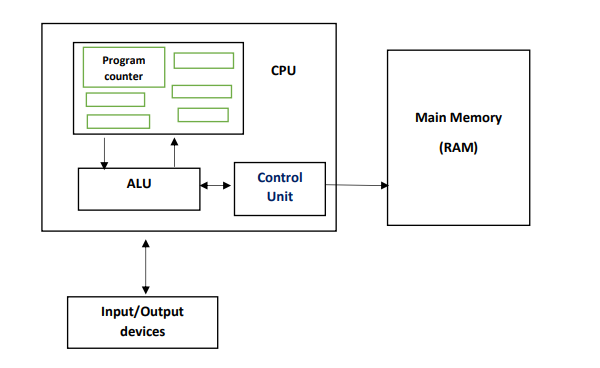

Basically, passing the fetched instructions to the Arithmetic and Logic unit in order to understand the data and instructions are called as decoding

Execution

Then the data operands require to execute the instructions are fetched from memory are placed into the program counter registers in CPU.

• As further ALU is the place who does the operation.

- It needs both data operands and instructions.

- Ex- 50+20 can be done inside ALU. For that 50 and 20 will be data which are getting from memory and the addition is the instruction which is also fetching from the main memory.

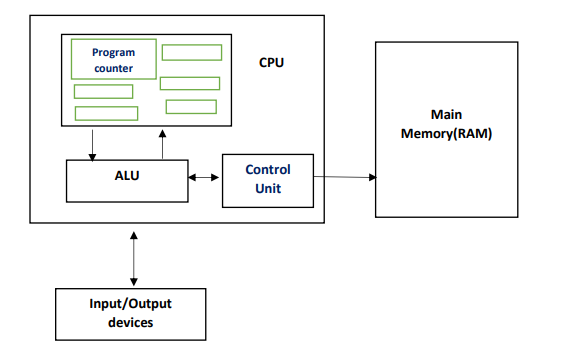

- Then that output will be stored in the program counter register in CPU. Main Memory(RAM) Input/Output devices Control Unit ALU Program counter CPU 5 However, this Von Neuman Architecture is having a disadvantage called Bottleneck. Basically in Von Neumann Architecture, there is a single data path between the CPU and the main memory. This reduces the performance due to the bottleneck. There the instructions and data cannot be passed at the same time and only one instruction at a time can be passed. If a cpu needs to do an operation on some data items in the main memory it should pass the data across the bus into the cpu. When the operation is over it needs to pass the output to the memory from the same bus as well. The amount of data that a particular bus can pass at a time is smaller in here. To reduce that now there is a cache memory in between it and if a user needs to access data he can use cache memory to access the data because there might get a traffic when transferring data directly from the memory and the cpu.

Harvard Architecture.

Due to the bottleneck of Von Neumann Architecture, the Harvard Architecture came.

• According to the Harvard architecture there are two memories called the instruction memory and the data memory. Therefore, this Harvard architecture is having the separation in between the code and the data. Therefore, the CPU can access instructions and read/write data at the same time. This architecture is more complicated than the previous one. But the separation of pipelines eliminates the bottleneck problem which the Von Neumann architecture addressed.

- This architecture has a less data traffic and the performance is higher than the previous one.

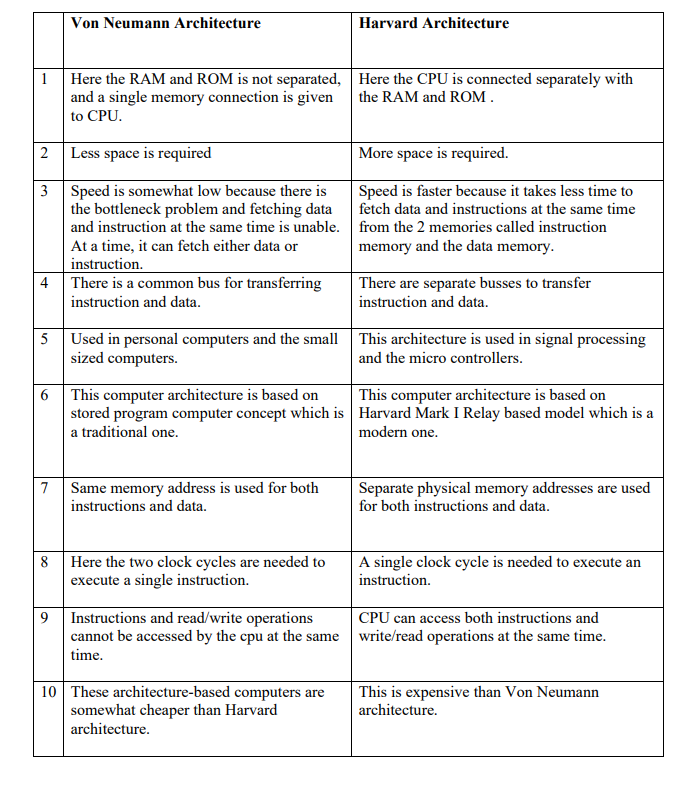

Distinguish between Von Neumann and Harvard

The Non von Neumann Architecture

The traditional stored program computers have faced for many changes and improvements in the past years. From these improvements and the developments It is added specialized busses, cache memories in order to reduce the data traffic, and floating-point units are added. But for the massive improvements it should replace the von Neumann architecture. For that we can add a processor. Present architectures like Harvard architectures there are separate busses for the data and instructions. The other non-Von Neumann models provide special purpose processors to disable work from the CPU. Parallel processing allows the computers to work on subparts of a particular problem concurrently. Multicore processors have two or more processor cores sharing single die. Each core is having its registers and the ALU whereas each processor shares the other resources and the memory. As instances in order to increase the throughput in late 1960’s the high-performance computers are included with two processors. Lately then supercomputers were invented with 32 processors. Then with the use of 1000 processors the supercomputers were invented in 1980’s. 1999 IBM introduced Blue Gene system with the use of 1 million processors. As the more examples for the Non Von Neuman model we can take,

• Quantum computers

• Optical computers

- Cell processors

- Analog computers

- Neural networks

- MIMD architecture

- DNA

Hope you got a knowledge regarding the Von Neumann, Harvard and non Von Neumann architectures.

Thank you.